VHDL for FPGA Design/4-Bit Adder

< VHDL for FPGA Design4-Bit Adder with Carry Out VHDL Code

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity Adder is

port

(

nibble1, nibble2 : in unsigned(3 downto 0);

sum : out unsigned(3 downto 0);

carry_out : out std_logic

);

end entity Adder;

architecture Behavioral of Adder is

signal temp : unsigned(4 downto 0);

begin

temp <= ("0" & nibble1) + nibble2;

-- OR use the following syntax:

-- temp <= ('0' & nibble1) + ('0' & nibble2);

sum <= temp(3 downto 0);

carry_out <= temp(4);

end architecture Behavioral;

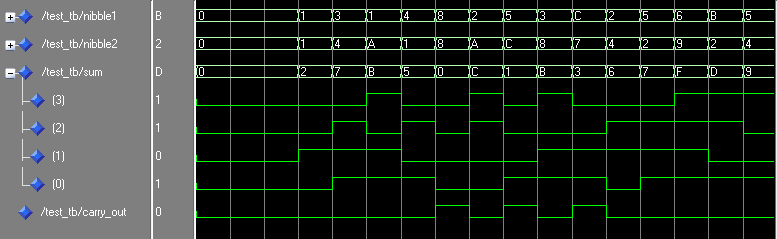

Simulation Waveform

library ieee; use ieee.std_logic_1164.all; use work.all; entity adder4b is port (a,b:in std_logic_vector(3 downto 0); cin:in std_logic; cout:out std_logic; s:out std_logic_vector(3 downto 0)); END adder4b; architecture arch12 of adder is signal y:std_logic_vector(4 downto 0); begin y(0)<= cin; cout<=y(4); --u:for i in 0 to 3 generate --p:entity work.FA(arch) port map(a,b,c,s,r=>y(i+1)); p0:entity work.FA(arch) port map(a=>a(0),b=>b(0),c=>y(0),s=>s(0),r=>y(1)); p1:entity work.FA(arch) port map(a=>a(1),b=>b(1),c=>y(1),s=>s(1),r=>y(2)); p2:entity work.FA(arch) port map(a=>a(2),b=>b(2),c=>y(2),s=>s(2),r=>y(3)); p3:entity work.FA(arch) port map(a=>a(3),b=>b(3),c=>y(3),s=>s(3),r=>y(4)); --end generate;

This article is issued from Wikibooks. The text is licensed under Creative Commons - Attribution - Sharealike. Additional terms may apply for the media files.